纳米增材制制工艺可大幅降低芯片出产成本

团队暗示,上述工艺流程存正在几个较着错误谬误。起首是成本昂扬。目前,先辈电子设备和芯片制制设备的建形成本约为200亿至400亿美元,每年的运营成本也高达10亿美元。其次是采

团队暗示,上述工艺流程存正在几个较着错误谬误。起首是成本昂扬。目前,先辈电子设备和芯片制制设备的建形成本约为200亿至400亿美元,每年的运营成本也高达10亿美元。其次是采

Source:

团队暗示,上述工艺流程存正在几个较着错误谬误。起首是成本昂扬。目前,先辈电子设备和芯片制制设备的建形成本约为200亿至400亿美元,每年的运营成本也高达10亿美元。其次是采用现无方法制制芯片需要半年到一年时间,测试后的点窜同样需要这么长时间。第三是该流程能耗极高。

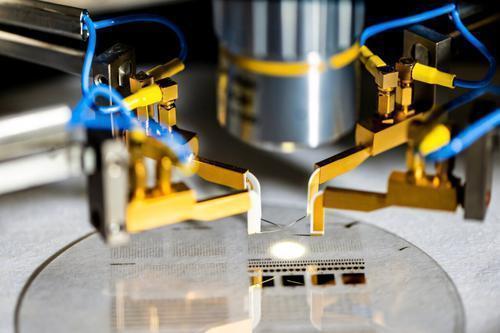

据美国官网近日报道,该校研究团队开辟出一种新工艺及打印设备,能正在纳米标准上更高效地制制先辈的电子产物和芯片,其制形成本仅为保守手艺的1%。

保守微电子制制的根基流程是将材料堆积到薄膜内,再“蚀刻”掉多余部门。每层材料形成电子电的一部门,多层材料叠加建立,最终构成一个微处置器或存储芯片。并且。

相关信息